Description

daiteq provides arithmetic extensions for optimal computation of floating-point as well as fixed-point arithmetic in LEON and NOEL-V processors, targetting areas of software-defined radio algorithms and image processing algorithms. Technology demos are available for the Xilinx, Microchip and NanoXplore FPGAs.

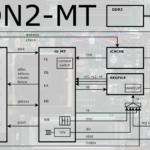

- LEON2-MT

Competences and capabilities

- Design and implementation of LEON and NOEL-V systems.

- Implementation in NanoXplore, Microchip, Xilinx.

- Floating-point computations. Support for GNSS processing in LEON2-FT and NOEL-V.

- Hardware accelerators for image processing applications and other data-parallel applications.

- Design of FPGA-based controllers.

- Benchmarking of embedded processors and systems.

Products

- at SIMD-within-a-register (SWAR) extensions for LEON2-FT and NOEL-V. Target areas: GNSS, image processing, ANN, data encryption.

- Floating-point unit for LEON2-FT, LEON3, NOEL-V. The daiteq FPU supports a variety of floating-point formats, including packed formats, configurable synthesis time.

- llvm extensions for SPARC and RISC-V. The extensions support the daiteq floating-point unit and the SWAR unit in LEON and NOEL-V processors.

- FMC-SRAM board for NanoXplore, Microchip and Xilinx FPGA demo boards.

Major Space Projects & References

- TRP/ITI: Multi-threaded processor for space applications. Instruction set extensions for micro-threading in LEON2-FT

- EO: METOP SG: Design review of the 3MI Filter Wheel Controller Design.

- GSTP: ESA IP core extensions. Configurable floating-point and integer SIMD-unit for LEON2-FT and NOEL-V. Techmap for NanoXplore BRAVE FPGAs.

- EO: AGGA-4 IP core conversion. Modification of the AGGA-4 IP core to suit FPGA targets.

Space Related Equipment, Labs & Certificates

N/A